A draft of Level 2 protection was presented at the same time. Kerry McGuire Balanza 11 May 2010. This limitation was removed in the ARMv3 series, which has a 32-bit address space, and several additional generations up to ARMv7 remained 32-bit. ARM invested in Palmchip Corporation in 1997 to provide system on chip platforms and to enter into the disk drive market. PSA Certified offers a multi-level security evaluation scheme for chip vendors, OS providers and IoT device makers. Main article: 1981 was also the year that the was introduced. ARMv7-A architecture optionally includes the divide instructions. Complicating price matters, a merchant foundry that holds an ARM licence, such as Samsung or Fujitsu, can offer fab customers reduced licensing costs. External links [ ] Wikimedia Commons has media related to. Companies that have developed chips with cores designed by Arm Holdings include 's subsidiary, , , now: , , , , , now , , , [ — ] , , , , , , , and. — a 32-register architecture based heavily on a 32-bit ARM• ARMv9 [ ] ARMv9-A [ ] Announced in March 2021, the updated architecture places a focus on secure execution and compartmentalisation. Neon can execute MP3 audio decoding on CPUs running at 10 MHz, and can run the AMR speech codec at 13 MHz. Arm's core designs are also used in chips that support many common network-related technologies in smartphones: , and , in addition to corresponding equipment such as , , and network providers' cellular. , the building blocks of 2005 [ ]• Intel later developed its own high performance implementation named XScale, which it has since sold to. a feeling of weakness in the affected arm• 5 times faster than their SPARC chips, "with double-precision floating-point performance of 2. Schor, David 25 August 2018. Large Physical Address Extension LPAE [ ] The Large Physical Address Extension LPAE , which extends the physical address size from 32 bits to 40 bits, was added to the ARMv7-A architecture in 2011. User mode: The only non-privileged mode. It also helps to distribute force from the upper part of the arm to the rest of the skeleton. Superficial layer• a sensation of numbness or tingling in the arm or hand• The main artery in the arm is the. In Thumb, the 16-bit opcodes have less functionality. Whether the Main Stack Pointer MSP or Process Stack Pointer PSP is used can also be specified in CONTROL register with privileged access. In 2013, 10 billion were produced and "ARM-based chips are found in nearly 60 percent of the world's mobile devices". This section needs additional citations for. System Controllers: CoreLink GIC-400, CoreLink GIC-500, PL192 VIC, BP141 TrustZone Memory Wrapper, CoreLink TZC-400, CoreLink L2C-310, CoreLink MMU-500, BP140 Memory Interface• You have nearly unlimited choices on information and arrangement in reports. Axys Design Automation, a developer of design tools and Artisan Components, a designer of physical IP : libraries, memory compilers, etc. Embedded hardware, such as the , typically have a small amount of RAM accessible with a full 32-bit datapath; the majority is accessed via a 16-bit or narrower secondary datapath. The arm, as can be seen here, formed one component of Clinical significance [ ] The is clinically important for and for measurement. Since 2016, it has been owned by conglomerate. Obsidian Software Inc. HiSilicon ,• VFPv3-F16 Uncommon; it supports as a storage format. Recently introduced, page mode allowed subsequent accesses of memory to run twice as fast if they were roughly in the same location, or "page". 在ARM架構的機器中,週邊裝置連接處理器的方式,通常透過將裝置的實體暫存器對應到ARM的記憶體空間、輔助處理器空間,或是連接到另外依序接上處理器的裝置(如匯流排)。

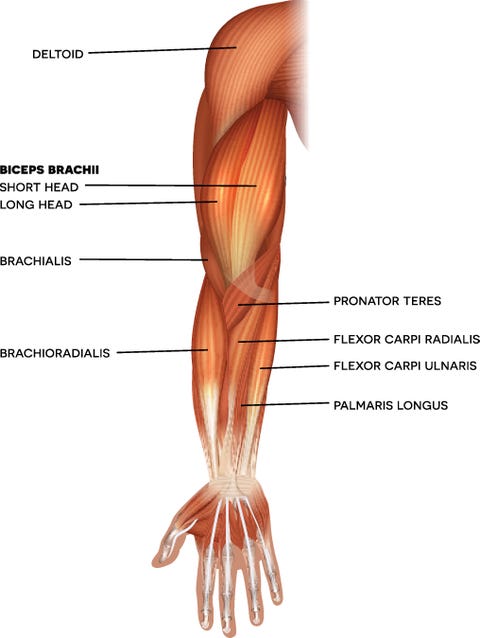

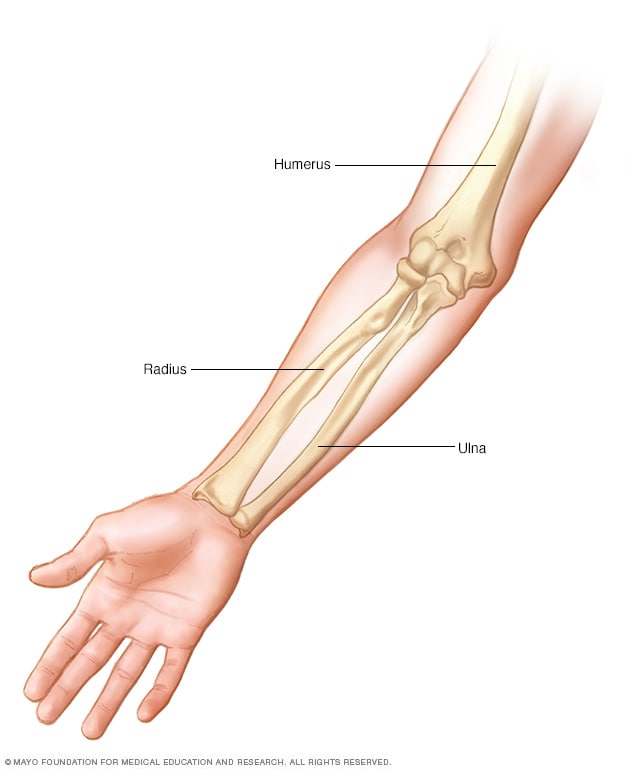

They eventually join the axillary vein. Cutress, Dr Ian 22 June 2020. — runs 32-bit " and 32-bit ARM applications", as well as native ARM64 desktop apps. The ARM2 was roughly seven times the performance of a typical 7 MHz 68000-based system like the or. Biceps brachii. Benefits of an ARM• Enabled in some but not all products, AMD's include a Cortex-A5 processor for handling secure processing. The graphics system was also simplified based on the same set of underlying assumptions about memory and timing. The Ares Platform includes the Neoverse N1 and Neoverse E1. when its parent company, plc, floated on the and in 1998. MX1)、Hewlett-Packard 、、、 )、導航裝置(mid—late 2000s)、導航裝置 ARM922T 恩智浦半導體 ARM926EJ-S Nuvoton , 德州儀器1710、OMAP1610、OMAP1611、OMAP1612、OMAP-L137、OMAP-L138; MSM6100、MSM6125、MSM6225、MSM6245、MSM6250、MSM6255A、MSM6260、MSM6275、MSM6280、MSM6300、MSM6500、MSM6800; 、i. No previous supercomputer has ever led all four rankings at once. November 2020, Mayank Sharma 26. Ashok Bindra 28 July 2011. Arduino [ ] In October 2017, announced its partnership with ARM. The , from C5, C6, C7, is the main supplier of muscles of the anterior compartment. Each of the three trunks contains an anterior and posterior division, meaning there are six divisions in total. Sinofsky, Steven. GPUs: ,. Clarke, Peter 23 July 2010. 's , Denver 2 and used in their SoCs. At the same time, the ARM instruction set was extended to maintain equivalent functionality in both instruction sets. Each arm contains several important veins and arteries. Each Astra node will feature two 28-core ThunderX2 processors running at 2. The Cray XC50-series supercomputer for the is called Isambard, named after. The difference between the ARM7DI and ARM7DMI cores, for example, was an improved multiplier; hence the added "M". The three-day virtual conference will serve up insights into the latest technology trends, give you an opportunity to up-level your skills in technical sessions and hands-on workshops, and offer up the chance to network with like-minded software developers and hardware designers. Superficial layer• Technologies, an company that developed a suite of tools that automate the process of IP configuration and IP integration 2015 [ ]• Thus by running the CPU at 1 MHz, the video system could read data during those down times, taking up the total 2 MHz of the RAM. CPU modes [ ] Except in the M-profile, the 32-bit ARM architecture specifies several CPU modes, depending on the implemented architecture features. All chips in the Cortex-A series, Cortex-R series, and ARM11 series support both "ARM instruction set state" and "Thumb instruction set state", while chips in the series support only the Thumb instruction set. Archived from on 11 September 2011. For ARM7 and ARM9 core generations, EmbeddedICE over JTAG was a de facto debug standard, though not architecturally guaranteed. They also considered the new 32-bit designs, but these were even more expensive and had the same issues with support chips. Clarke, Peter 1 November 2013. The basilic vein travels on the medial side of the arm and terminates at the level of the seventh rib. formerly Raspbian• Those needing to learn how to speak the languages of owners, residents, and investors• Symptoms of a vascular issue affecting the arm include:• 's primary business is selling , which licensees use to create MCUs , , and based on those cores. (英文) (,存于)• Many muscles and ligaments in the arm are attached to the humerus. forearm• Schor, David 20 February 2019. The Thumb instruction set is referred to as "T32" and has no 64-bit counterpart. Hide all calculated or all original data columns with one command when creating the view. Devices such as the ARM Cortex-A8 and Cortex-A9 support 128-bit vectors, but will execute with 64 bits at a time, whereas newer Cortex-A15 devices can execute 128 bits at a time. History [ ] Name [ ] The acronym ARM was first used in 1983 and originally stood for "Acorn RISC Machine". Archived from on 1 August 2017. Forearm The forearm is the area between the elbow joint and the wrist. delivers a description of the chosen ARM core, along with an abstracted simulation model and test programs to aid design integration and verification. Homogeneity of variance test during AOV• On 19 November, ARM, alongside , , , , and , founded the , to promote interests and development in. View subsample means within plot data editor• The in-depth knowledge gained from designing the instruction set enabled the code to be very dense, making ARM BBC BASIC an extremely good test for any ARM emulator. The is also called the shoulder blade. Subclavian artery. 安全性擴充(TrustZone) [ ] TrustZone技術出現在ARMv6KZ以及較晚期的應用核心架構中。

/armpainfinal-01-5c86a3fa46e0fb0001a0bebd.png)